Let’s say I haven’t had an orgasm watching Sony announcements for many years, but oh boy this one is just too good.

Luckily Sony has published a few papers about a prototype with 6.9um pixels around 2018 (not far from A9III’s 6um pixel), otherwise we wouldn’t know how powerful this new architecture actually is. The funny thing is that you can no longer measure the readout speed of a global shutter sensor.

Traditional global image sensors first capture the image and then store the information in the analog domain, waiting for their turn to do AD-conversion one by one. The problem is that the sensor can still absorb some light even after the exposure is supposed to be finished, or let’s say they just can’t close their “shutter” completely. Therefore, they need some extra measures to shield the sensor from “parasitic light”, which reduces the image quality in one way or another.

Sony on the other hand, has built a tiny Single-Slope ADC into each pixel, which is fxxking crazy. So the sensor has two stacked layers, one with 24 million pixels and one with 24 million ADCs, logic, I/O, SRAM and some other stuff. There are also at least 48 million Cu-Cu connections between the two layers. The prototype shown below only has 1.46M pixels but the principle is the same:

So basically there are no more waiting in the queue. The signal from all pixels is converted to the digital domain at the same time. We can call it the “digital global shutter”.

On paper this basically get rid of all the issues of traditional “analog global shutters”. Well just on paper… there is obviously some issues (ISO250!) that we’ll address later.

The sensor is not just about global shutter though. Traditional column-parallel ADC sensors only has a few thousand ADCs. This thing has 24 fxxking million. Even though each one is tiny and slow, the sheer number has made sure that this sensor is just insanely fast. The prototype has a readout speed of 660FPS!

And this is actually limited by the IO speed. The ADC can complete a cycle in 0.39ms. So in theory the maximum speed can be as fast as 2400FPS!

Another wonderful thing is that there is no such thing as a resolution-speed trade-off anymore. In conventional column-parallel sensors more pixels in total = more pixels for each ADC to handle = slower speed. In pixel-parallel sensors more pixels = more ADCs = the same speed whatsoever. So I assume that A9III’s sensor is in the same 2500FPS ballpark or even better.

Let’s say with this architecture Sony would never have to worry about the speed again for the next decade or two.

So speed is no longer the concern, but what about the resolution?

Well that’s the main challenge here. First of all you’ll have to squeeze a tiny ADC into the pixel. Single-slope ADC is probably the tiniest ADC structure due to a lot of resource sharing but there is still a comparator + a 14-bit counter and some other stuff. For smaller format it’s even worse. 6um pixel = 10MP for APS-C or 10 pixels for smartphones. So finally we have some new technology that discriminates against smaller sensors lol.

The good news is that you can always shrink your ADC with more advanced process node, and Sony still has a big room for improvement since the prototype only uses the 65nm process node for the logic chip:

Sony also published a detailed paper about A1’s sensor, which has a full-frame size 40nm chip stacked on the 90nm pixel layer. I assume that A9III is also using 40nm. Anyway, if they can make a 6.9um pixel with 65nm then I think 4.2um (50MP) with something like 28nm isn’t really a pipe dream. Sony was already doing 28nm chips for smartphone sensors back in 2016:

There is a second issue though. 24 million ADCs working at the same time is going to create a huge peak current, which could be an issue for the power supply. The total power consumption is not the main concern here. It’s like you’re trying to move 100 bricks from A to B. You can either do 100 runs, each run moving only 1 brick, or do only one run with all the bricks. The result is the same but it depends on whether you can handle the total weight of 100 bricks. And even if you’re operating at 1FPS the peak current is still there. Sony has made quite a lot of effort to reduce the current consumption for each ADC. The average consumption can be as low as 1.7nA for a 660FPS output speed. The funny thing is that due to their immense effort to drop the peak current, it looks like this sensor is actually more efficient than the A1 sensor. Based on the number provided in the paper, if you increase the resolution to 50MP and drop the speed to 44FPS (just like A1’s sensor), then the power consumption is going to be 1.73W, much lower than A1 (2.76W):

|  |

This is not reflected in the battery life of the final products though. First of all nobody is doing full speed output when you’re just looking at the viewfinder. And the sensor’s power consumption is just a small part of the total consumption. A1’s power consumption is actually 4.3W when using the EVF.

Anyway, it looks like the new technology isn’t that power hungry, which is good news. But you probably noticed that it has two power consumption number. Actually one is for the low power/high noise mode and one is for the low noise/high power mode. Now, here comes the bad news…

The Image Quality Sucks?

Even in the high-power mode the read noise is still 5 times larger than A1. So you have more ADCs now but it looks like they’re not as capable as those big column ADC that can utilize more area or more current.

But this is not even the worst part. The full well capacity is only 16.6k e-. A1’s FWC is 60k e- and the pixel size is much smaller! It’s basically an ISO1000 sensor vs an ISO100 sensor!

Sony explained that the FWC is low only because the DAC in the prototype isn’t top notch, it’s not the pixel’s fault blablabla. But as you can see… A9III has a base ISO of 250, and also no dual-gain. Ouch!

My guess is that the reason behind the low FWC is that the pixel design is actually quite different:

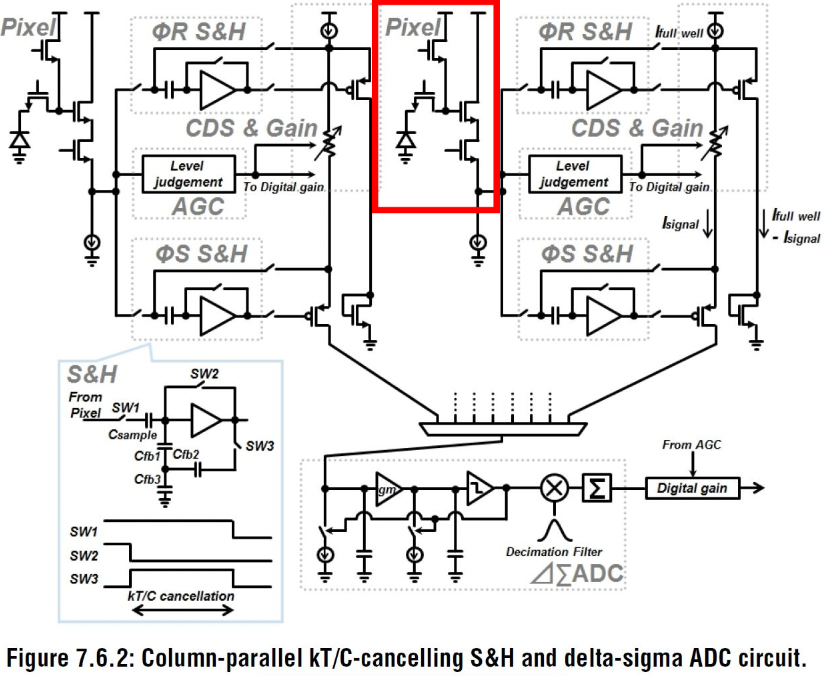

This part is difficult to explain to people who’s not familiar with analog circuit design but let’s say a small part of the ADC is actually in the pixel layer instead of the digital layer. The three transistors on the left are the input pair and the biasing current of a simple comparator. The other half of this comparator is in the digital layer, connected via two cu-cu nodes.

If you take a look at A1’s pixel design, which is your typical 4T structure, it’s much simpler (the red part):

These three extra transistors could also be very large due to the need to drop the current consumption. It’s difficult to tell because Sony is operating them in the sub-threshold region where everything changes exponentially. It’s possible that these transistors are taking too much space and drops the FWC. But at this point it’s really just my wild guess.

If my guess is correct, then first of all… ISO250 just sucks. It’s going to be a deal breaker for many people. I guess our digital global shutter sensor is just like their analog cousins that have poor image quality. The main difference is actually the speed. It also means shrinking the pixel size might be quite difficult. You’ll need better process technology for both the digital layer and the pixel layer, which kinda defeats the purpose of making a stacked sensor. As far as I know Sony’s pixel layer has been stuck with 90nm for many years even for smartphones.

A potential fix is to the ISO 250 issue is to use some on-chip multi-frame stacking to achieve higher dynamic range. As I said the ADC can be as fast as 2500FPS internally so if you have some integrated memories and processing circuit then you can finish a 4-frame integration in merely 1/600s. 1/600s is certainly not ideal for fast moving subject but probably good enough for most situations, better than nothing after all. Practically, for birding or sport shooting you can rarely achieve a high shutter speed + low ISO combination anyway. Sony has indeed introduced a new multi-frame stacking feature in A9III, with some interesting description like “possible to shoot wildlife at higher shutter speed”. But it’s not really on-chip (extra work flow with made in Japan software lol), and it remains to be seen how it works and what’s the integration time.

Anyway… even with such a huge flaw, let’s say global shutter is regarded as “the Holy Grail or photography” for a very good reason, and the speed aspect of the new technology is certainly appealing. But for now, I’d say the price is just too steep. I was expecting something like $4500. SonyAlphaRumors has destroyed my dream. If I had $6000 to burn on a camera then I’d rather buy an A1II. A1’s sensor is still a beast of its own even though it’s not a global shutter sensor. The major downside is that it doesn’t have the fancy 4-axis screen or all the latest software. Sony has basically given A9III everything they could, and I expect no less from A1II.